**David Vernon**

The goal of this course is to introduce hardware and software design techniques and issues for interfacing computers and peripheral devices

- Course Contents

- □ Digital data communication standards serial communications

- Devices

- RS232

- RS422

- Handshaking

- Implementation of RS232 on a PC

- ☐ Universal Serial Bus (USB)

- USB standards

- Types and elements of USB transfers

- Development procedure for USB applications

- Course Contents

- □ Parallel Communications

- General Purpose Interface Bus (GPIB)

- GPIB signals and lines

- Handshaking and interface management

- Implementation of a GPIB on a PC

- Course Contents

- Digital and Analogue Interfacing

- Digital Interfacing

- o Digital I/O ports

- o Interfacing external signals to digital I/O ports

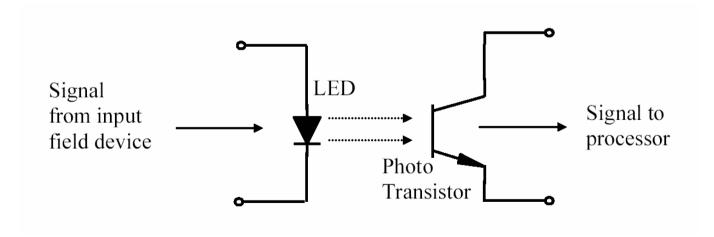

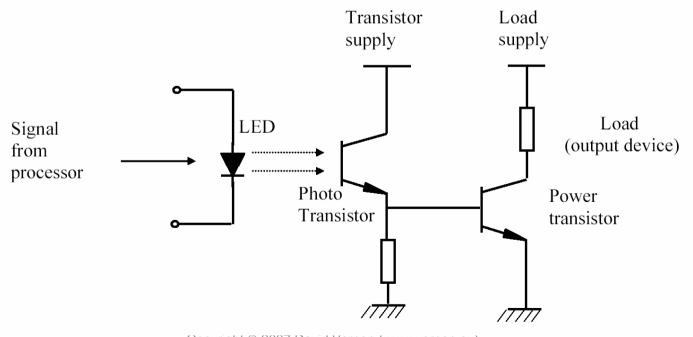

- o Optical isolation

- Analogue Interfacing

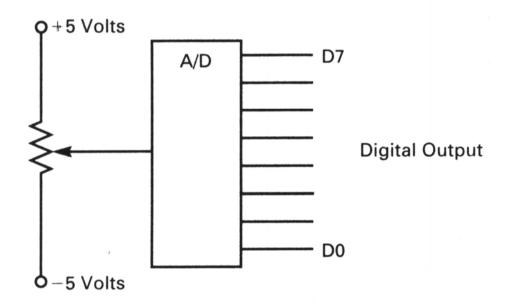

- o Revision of A/D and D/A conversion techniques

- o Multiplexing

- o Analogue I/O cards

- o Data acquisition and control using a PC

#### Course Texts:

PC Interfacing

Communications and

Windows Programming,

William Buchanan, Addison

Wesley

Microcomputer Interfacing and Applications,

M. A. Mustafa, Newnes

Course Loading: 0.5 Module

```

1 Lecture each week (weeks 1, 2, 3, ...)

```

- 1 Tutorial every second week (weeks 3, 5, 7, 10, 12, 14)

- 1 Lab demonstration every fourth week (weeks 4, 11, 15)

- 1 Assignment, due on the last day of week 15 (22<sup>nd</sup> Dec.)

#### Motivation

- The need for computer interfacing

- Advanced control applications need flexible processing power, i.e. computers

- Control data has to be input and output

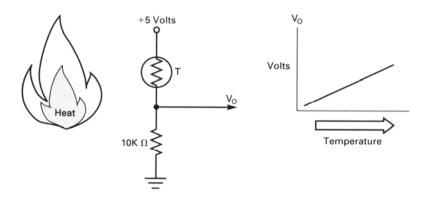

- Input from sensors (speed, acceleration, temperature, ..)

- Output to actuators (motors, switches, valves, ...)

- Examples:

- Robotics

- Industrial process control

- Advantages of using computers for Data Acquisition & Control

- High speed

- Programming flexibility (compared with hard-wired logic)

- Mass storage of data

- Data analysis and visualization

- Low cost (relatively)

#### Issues:

- Input vs output (direction)

- Communication between devices

- Data acquisition

- Device control

- ☐ Digital vs Analogue data (modality)

- Signal levels (may be a need for signal conditioning)

- Analogue to digital conversion (ADC)

- Digital to analogue conversion (DAC)

- ☐ Serial vs parallel (mechanism)

- Speed, distance, number of required lines, standard I/F

- ☐ Polled vs interrupt driven (mechanism)

- Simplicity, processor efficiency

- History

- ☐ Early '70s: Intel 4004

- 4 bit of data (nibble)

- 2000 transistors

- 46 instructions

- 4kB program code

- 1kB data

- **□** 1974 : 8008, 8080, 8085

- 8008: 14-bit address space (16kB memory)

- 8080: 16-bit address space (64kB memory)

#### History

- ☐ Early 80s: 8086 Major revolution in processing power

- 16-bit data bus

- 20 bit address bus (1MB memory)

- PC & PC-XT

- 8088: Multiplexed 8-bit data bus

- 80286: enhance version (PC AT)

- History

- ☐ 1985: Intel 80386

- 32 bit data bus

- 32-bit address bus (4GB memory)

- □ 1986: Intel 80486

- Memory cache

- On-chip maths co-processor

- History

- 1990s: Pentium (P-5)

- 64-bit superscalar architecture

- MISD instruction pipeline (can execute more than one instruction at a time)

- 64-bit databus

- 32-bit address bus

- □ 2000s: Pentium II (P-6)

- Up to 4 processors on the same bus

- Single bit error detection and correction on the data-bus

- Multiple bit error detection

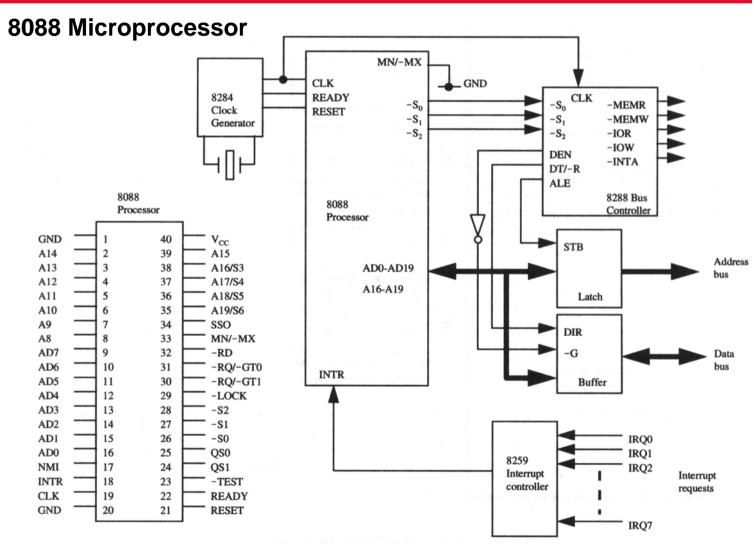

#### **\$808**

- 8288 bus controller generates signals based on the 8088 status lines \$\overline{\SO}\$, \$\overline{\SO}\$, \$\overline{\SO}\$.

- ☐ Main control signals:

- IOR (I/O Read): processor is reading from the content of the address which is on the I/O bus

- IOW (I/O Write): processor is writing the contents of the data bus to the address on the **I/O** bus

- MEMR (memory read): processor is reading from the contents of the address which is on the **address** bus

- MEMW (memory write): processor is writing the contents of the data bus to the address which is on the address bus

- INTA (interrupt acknowledge): used by the processor to acknowledge an interrupt (sent via the 8259 interrupt controller)

- **\$808**

- ☐ Two address spaces:

- Memory space

- I/O space

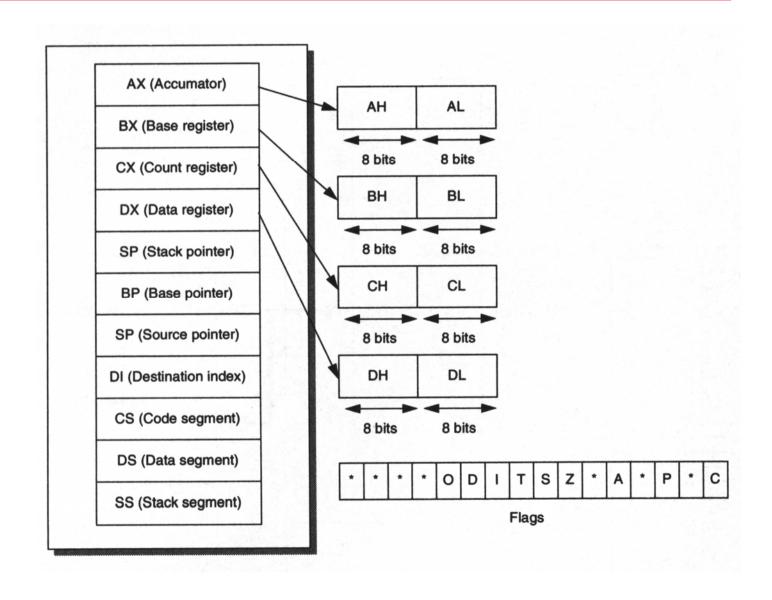

- ☐ Registers

- 4 general purpose registers

- AX Accumulator (all I/O operations & some arithmetic)

- BX base register (can be used as an address register)

- CX count register (e.g. loops)

- DX data register (some I/O and when multiplying & dividing)

- 4 addressing registers

- SI source index (extended addressing commands)

- DI destination index (used in some addressing modes)

- BP base pointer

- SP stack pointer

- **\$808**

- Registers

- Status registers registers

- IP instruction pointer (contains address of next instruction to be executed)

- F flag register (with bits set depending on conditions or results of operations, e.g. is the result negative)

- Segment registers (16 bits 64kB)

- CS register: code segment; defines the memory location where the code/instructions are stored

- DS register: data segment; defined where the data from the program will be stored

- SS register: stack segment; location of the stack

- ES register: extra segment

- All addresses are defined with respect to the segment registers

- 8086 has a segmented memory architecture

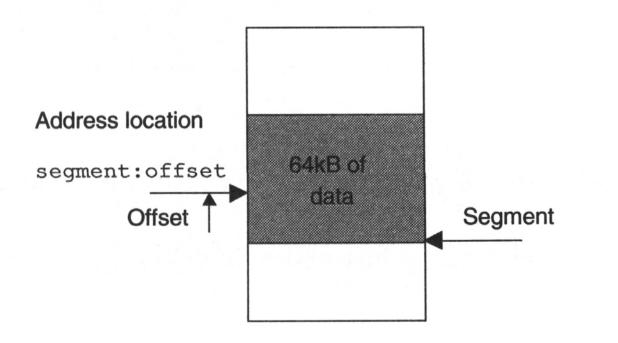

#### Memory segmentation

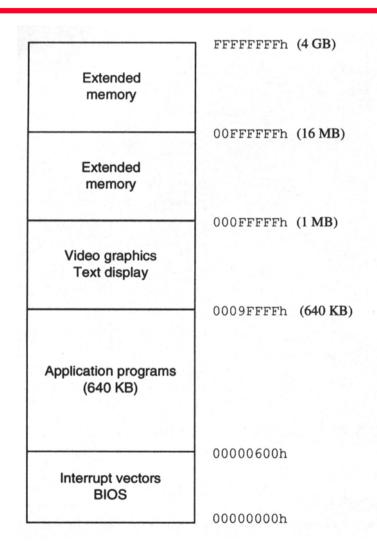

- 8086 has a 20-bit address space (1MB)

But can only directly address 64kB (16-bit address space)

I.e. it addresses the 1MB in chunks or segments

- A segmented memory address location is identified with a segment and an offset address (this is the logical address)

segment:offset 16 bits: 16 bits

- ☐ The actual physical address is calculated by shifting the segment address 4 bits to the left and adding the offset!

- What's the actual physical address in the following example?

Segment (2F84): Offset (0532):

Actual address:

| 0010 | 1111 | 1000 | 0100 | 0000 |   |

|------|------|------|------|------|---|

|      | 0000 | 0101 | 0011 | 0010 | , |

| 0010 | 1111 | 1101 | 0111 | 0010 |   |

- Memory segmentation

- ☐ In C the address 1234:9876h is specified as 0x12349876

- Near and far pointers

- A near pointer is a 16-bit pointer (64kB of data)

- A far pointer is a 20-bit pointer (1MB)

```

char far *ptr; /* declare a far pointer */

ptr = (char far *) 0x1234567; /*initialize a far pointer */

```

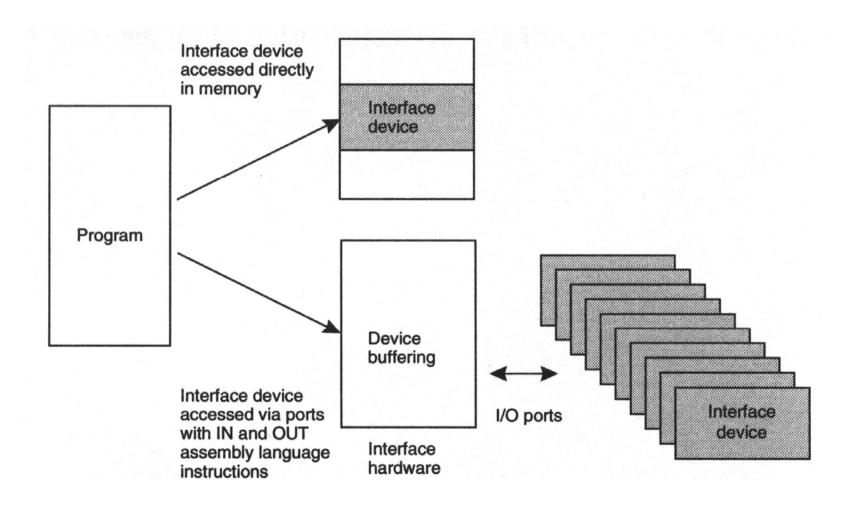

- Memory mapped I/O vs. Isolated I/O

- Memory mapped I/O

- Devices are mapped into the physical memory space

- Given real addresses on the address bus

- ☐ Isolated I/O

- Devices are mapped into a special isolated memory space

- Accessed via ports which act as a buffer between the processor and the device

- Accessed using the IN and OUT instructions (there are C equivalents)

- Isolated I/O uses 16-bit addressing from 0000h to FFFFh

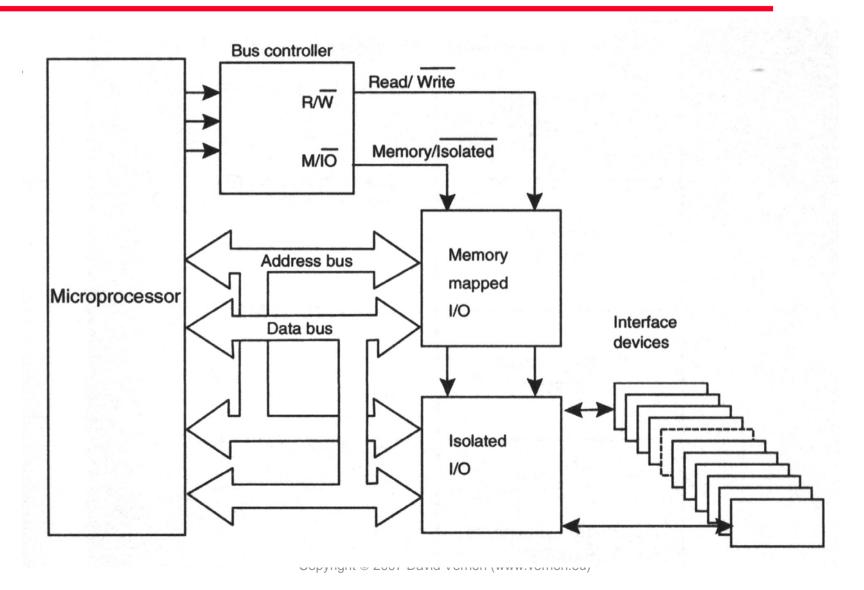

- ♦ 80x86 bus controller signals

- □ R/W

- Low when data is being written

- High when data is being read

- M/ĪO

- o Low when selecting isolated memory

- o High when selecting normal memory space

Typical PCommony Map rnon (www.vernon.eu)

#### Typical isolated I/O Memory Map

| 000h-01Fh | DMA controller                                  |

|-----------|-------------------------------------------------|

| 020h-021h | Programmable interrupt controller (PIC)         |

| 040h-05Fh | Counter/Timer                                   |

| 060h-07Fh | Digital I/O                                     |

| 080h-09Fh | DMA controller                                  |

| 0A0h-0BFh | NMI Reset                                       |

| 0C0h-0DFh | DMA controller                                  |

| 0E0h-0FFh | Math co-processor                               |

| 170h-178h | Hard disk (secondary IDE drive or CD-ROM drive) |

| 1F0h-1F8h | Hard disk (primary IDE drive)                   |

| 200h-20Fh | Game I/O adapter                                |

| 210h-217h | Expansion unit                                  |

| 278h-27Fh | Second parallel port (LPT2:)                    |

| 2F8h-2FFh | Second serial port (COM2:)                      |

| 300h-31Fh | Prototype card                                  |

| 378h-37Fh | Primary parallel port (LPT1:)                   |

| 380h-3AFh | SDLC interface                                  |

| 3A0h-3AFh | Primary binary synchronous port                 |

| 3B0h-3BFh | Graphics adapter                                |

| 3C0h-3DFh | Graphics adapter                                |

| 3F0h-3F7h | Floppy disk controller                          |

| 3F8h-3FFh | Primary serial port (COM1:)                     |

|           | Copyright © 2007 David Vernon (www.vernon.eu)   |

- Isolated I/O

- ☐ Inputting a byte from an I/O port

- Borland C

```

unsigned char value;

value = inportb(PORTADDRESS);

Prototyped in dos.h

```

■ Microsoft C++

```

unsigned char value;

value = _inp(PORTADDRESS);

```

- Isolated I/O

- ☐ Inputting a word from an I/O port

- Borland C

```

unsigned int value;

value = inport(PORTADDRESS);

Prototyped in dos.h

```

Microsoft C++

```

unsigned int value;

value = _inpw(PORTADDRESS);

```

- Isolated I/O

- ☐ Outputting a byte from an I/O port

- Borland C

```

unsigned char value;

outportb(PORTADDRESS, value);

Prototyped in dos.h

```

■ Microsoft C++

```

unsigned char value;

_outp(PORTADDRESS, value);

```

- Isolated I/O

- ☐ Outputting a word from an I/O port

- Borland C

```

unsigned int value;

outport(PORTADDRESS, value);

Prototyped in dos.h

```

■ Microsoft C++

```

unsigned int value;

_outw(PORTADDRESS, value);

```

#### Serial Interfaces: RS-232

- Serial data transmission is used for digital communication between

- Sensors and computers

- Computers and computers

- ☐ Computers and periperal devices (printer, stylus, mouse, ..)

- One of the most widely used communication techniques to interface external equipment

- Serial communciation protocol: 1 bit at a time, sequentially

- Parallel transmission: 1 word at a time (i.e. n bits in parallel)

- Advantages of serial transmission: very simple wiring

- Transmission Characteristics of RS-232

- maximum distance of 20 metres

- Maximum bit rate 19 600 bps

- Alternative serial communication standards:

- ☐ RS-422 (up to 10 Mbps over distance of 1.2km)

- ☐ USB-1 & USB-2

- ☐ IEEE 1394 (Firewire / iLink)

#### Serial Interfaces: RS-232

#### Electrical characteristics

- ☐ Logic 1: -3V to -25V; typically -12V

- Logic 0: +3v to +25V; typically +12V

- ☐ Any signal in the range -3V to +3V has an indeterminate logical state

- Quiescent or inactive state is -12V (i.e. logic 1)

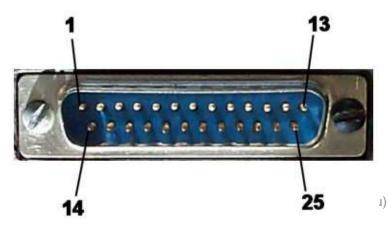

#### Connectors

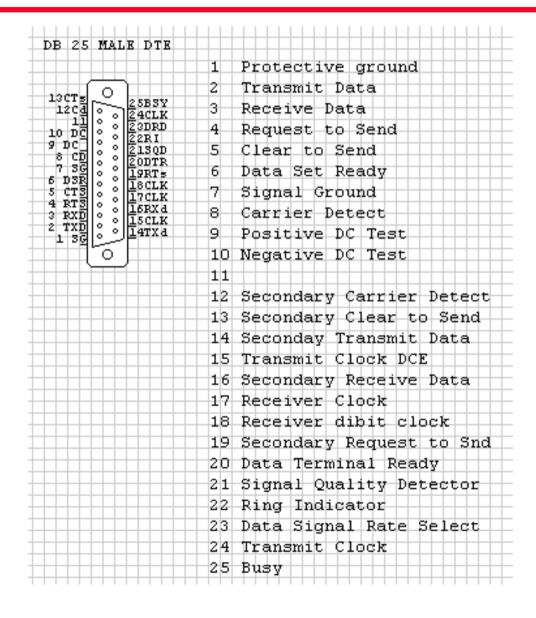

- ☐ DB25S is a 25 pin connector with full RS-232 functionality

- ☐ The computer socket has a female outer casing with male connecting pins

- The terminating cable connector has a male outer casing with female connecting pins

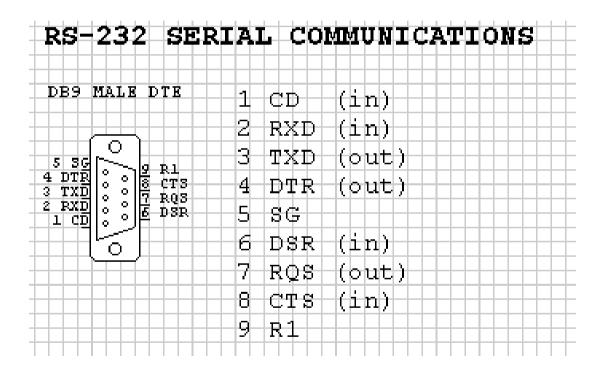

#### RS232 Pinout on DB25

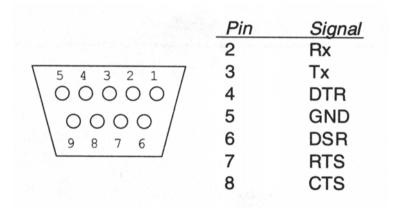

#### ◆ Connectors

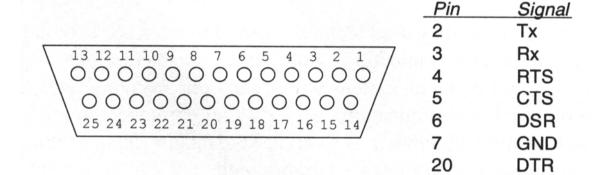

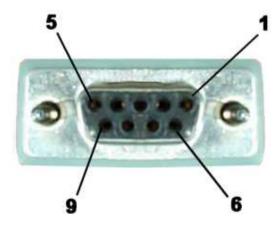

- □ DB9S is a 9 pin connector with reduced RS-232 functionality

- ☐ The computer socket has a female outer casing with male connecting pins

- ☐ The terminating cable connector has a male outer casing with female connecting pins

#### Connectors

- Most PCs use either a 9-pin connector for the primary (COM1:) serial port and a 25-pin for a secondary serial port (COM2:), or they use two 9-pin connectors

- Note: the 25-pin parallel port (LPT1:) is a 25-pin female connector on the PC and male on the cable

- ☐ The serial connector is male on the PC and female on the cable

- ☐ 25-to-9 in adaptors are available

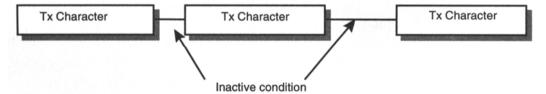

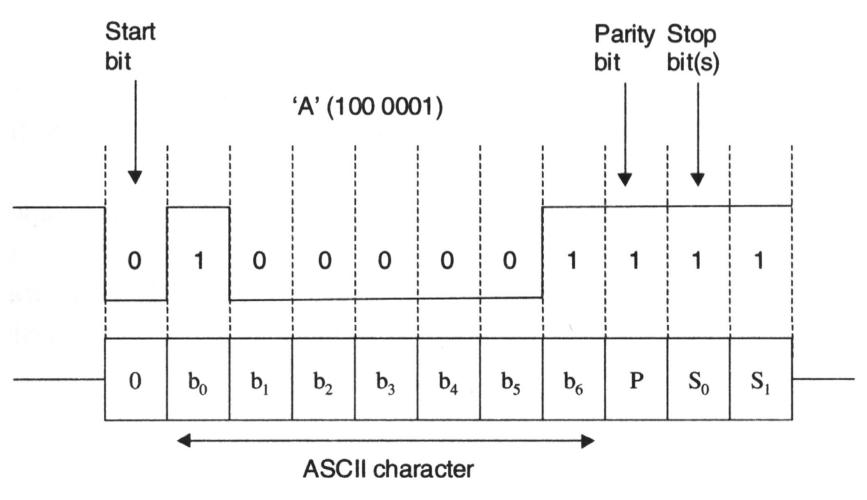

- ◆ Frame format

- ☐ RS-232 uses asynchronous communications

- ☐ Start-stop format

- Each character is transmitted one at a time

- Delay between each character: inactive time

- Inactive time: -12v logic level high

- Each character is frames by a start bit (0), 7 data bits, 1 parity bit, 2 stop bits

- ASCII coding is used

- Parity is either even, odd, none

- o Parity bit is set to make the total number of either even or odd (or not checked)

#### Frame format

- Both the transmitter and the receiver need to be set to the same bit-time interval (baud rate)

- ☐ Since RS-232 is asynchronous, clock rates don't have to be exactly synchronized

- ☐ There is an overhead in using asynchronous communication: the additional start and stop bits

- ☐ The advantages is that it makes communication very simple

#### Example

ASCII coding, even parity, 2 stop bits:

```

{inactive}11111 {start bit} 0 {'A'}1000001 {parity bit} 0

{stop bits} 11 {start bit}0 {'p'}0000111 {parity bit} 1

{stop bits}11 {inactive}11111111 {start bit}0

{'p'}0000111 {parity bit} 1 {stop bits}11 {inactive}11

{start bit}0 {'L'}0011001 {parity bit} 1 {stop bits}11

```

Message is 'AppL'

#### Parity

- Simple form of error coding

- A parity bit is added to transmitted data to make the number of 1s (in the data) either even (even parity) or odd (odd parity)

- ☐ A single parity bit can only detect an odd number of errors (why?)

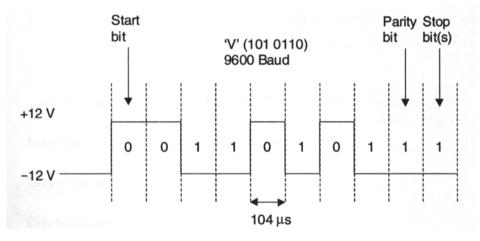

#### Baud Rate

- 11 bits required to send a single character (10 if one stop bits are used)

- ☐ Bit rate (bits/sec): actual rate at which bits are transmitted

- Baud rate: rate at which the signalling elements, used to represent bits, are transmitted

- Since one signalling element encodes one bit, both rates are identicial

- However, baud rates will differ from bit rates in modem communication

- ☐ Time period of each bit = 1/baud rate seconds

- Types of equipment

- ☐ DTE Data Terminal Equipment

- Originally applied to CRT terminals or other input devices

- Today, DTE mainly applies to a computer

- ☐ DCE Data Communication Equipment

- Originally applied to modems or similar communications equipment

- Still applies today

- A modem is a device that converts a digital signal (e.g. from an RS232 interface) to an analogue signal for transmission over a traditional telephone line (MODEM: MOdulator-DEModulator)

| Pin | Name                   | Abbrev | Functionality                                                                                                       |

|-----|------------------------|--------|---------------------------------------------------------------------------------------------------------------------|

| 1   | Frame Ground           | FG     | This ground normally connects the outer sheath of the cable to the earth ground                                     |

| 2   | Transmit Data          | TD     | Data is sent from the DTE (computer or terminal) to a DCE via TD                                                    |

| 3   | Receive Data           | RD     | Data is send from the DCE to a DTE via RD                                                                           |

| 4   | Request to Send        | RTS    | DTE sets this active when it is ready to transmit data                                                              |

| 5   | Clear to Send          | CTS    | DCE sets this active to inform the DTE that it is ready to receive data                                             |

| 6   | Data Set Ready         | DSR    | Signals that the DCE is ready to communicate                                                                        |

| 7   | Signal Ground          | SG     | All signals are referenced to the signal ground                                                                     |

| 20  | Data Terminal<br>Ready | DTR    | Signals that the DTE is ready to communicate RTS and CTS have no effect is DTR is not asserted and connected to DSR |

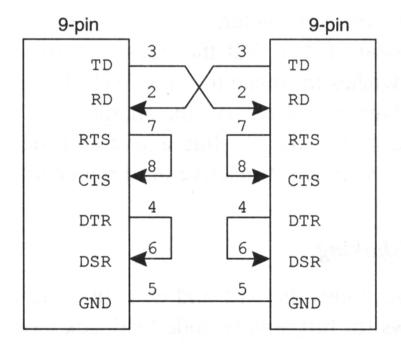

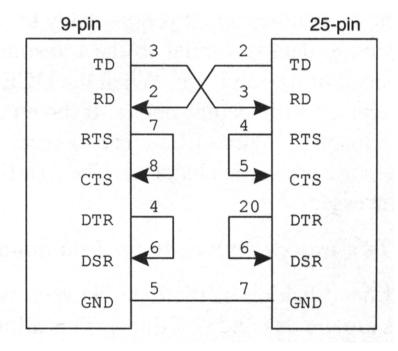

- Communication between two nodes

- Handshaking

- Hardware handshaking

- o RTS

- o CTS

- o DTR

- o DSR

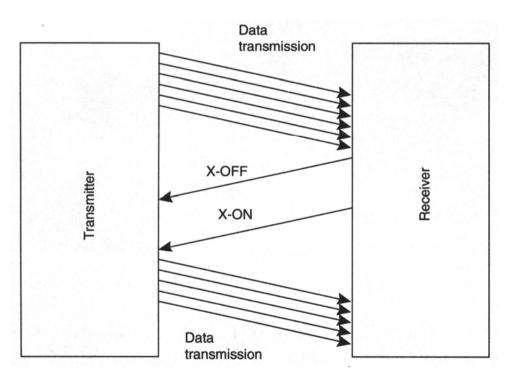

- Software handshaking

- o Sending special control characters X-OFF, X-On (ctrl-S, ctrl-Q)

- No handshaking

- o If no handshaking is used then the receiver must be able to read the received characters before the transmitter send more (otherwise the input buffer will be overwritten)

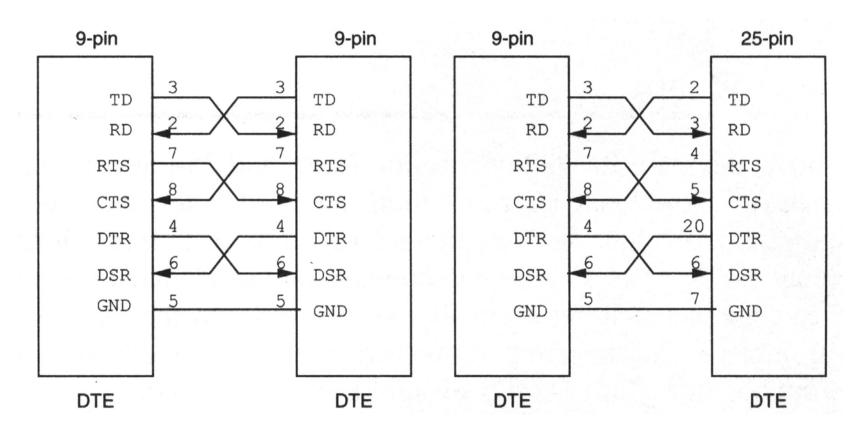

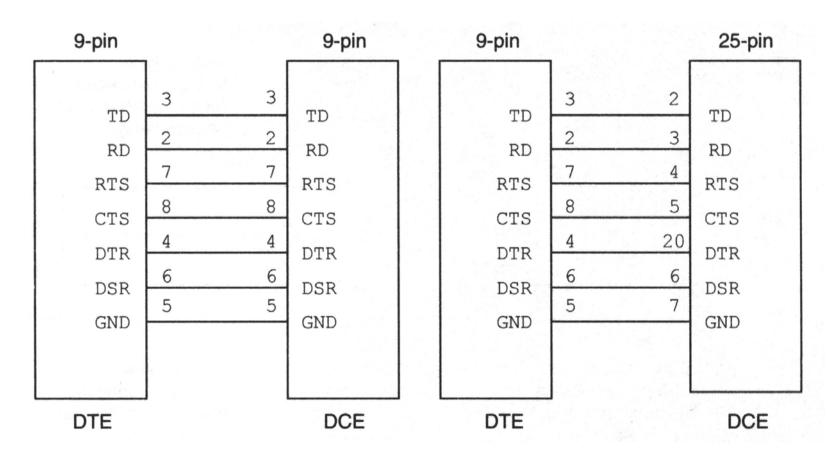

- ☐ Simple No Handshaking Connections

- note the loop-backs

- ☐ Simple No Handshaking Connections

- Advantage: no handshaking so fewer wires

- Disadvantage:

- o all handshaking has to be done by software (hence, more complex software)

- o The lack of the DTR means neither device knows whether the other device is powered up and ready for data tranfer

- Typically used when the devices can operate at much faster speeds than the communication channel

☐ Software handshaking

(Note that the software must recognize the X-ON and X-OFF characters and take the appropriate action)

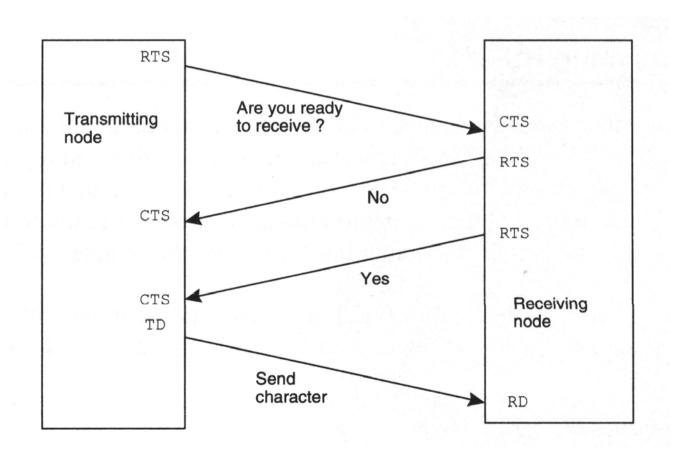

- Hardware handshaking

- To transmit:

- o Assert Transmitter RTS (high)

- o Wait until Transmitter CTS high

- o When receiver reads from its buffer (buffer empty), Receiver RTS goes high

- o ⇒Transmitter CTS, goes high

- o Transmitter sends data

- ☐ DTR and DSR are responsible for establishing the connection

- □ RTS and CTS are responsible for the data transfer

- ☐ Without an active DTR signal, the RTS and CTS signals have no effect

- Deactivating DTR or DSR breaks the connection

#### Hardware handshaking

#### Hardware handshaking

■ DTE to DCE connections for handshaking

- Typical System Connections

- Loop-back connections are used to test hardware (cf. program 15.1 in text)

- Null modem connections are used for communication (cf. programs send and receive; 15.2 & 15.3 in text)

- ☐ Types of error in serial communications

- Framing error: if the receiver has detected an invalid stop bit then the received serial character does not fit into the frame that the setup data format and the setup baud rate define. Thus the receiver has detected a framing error

- Break error: if the reception line is at a logical low for a longer time than usual then the receiver assumes that the connection to the transmitter is broken. The transmitter usually drives the line to a logical high level as long as no data is being transferred

- Overrun error: if data is arriving in the receiver faster than it is read from the receiver buffer register by the CPU, then a later received byte may overwrite the older data not yet read from the buffer.

- Parity error

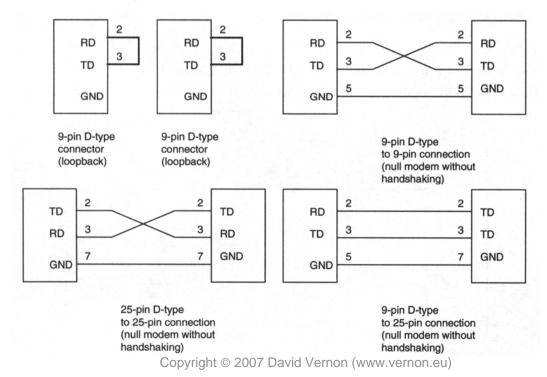

- Universal Asynchronous Receiver Transmitter (8250)

- ☐ UART transmits and receives characters using RS-232

- □ 40 pin IC

- Connection to the microprocessor is via D0-D7

- Microprocessor write: asserts DOSTR and DOSTR (high & low, respectively)

- Microprocessor *read*: asserts DISTR and DISTR (high & low, respectively)

- Universal Asynchronous Receiver Transmitter (8250)

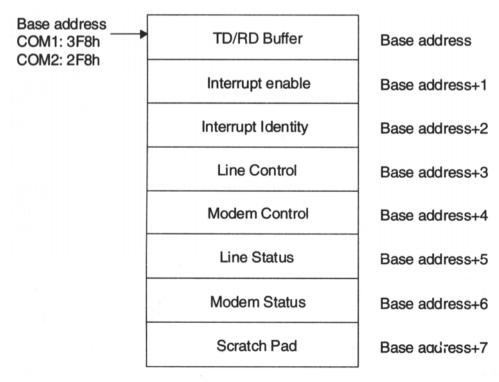

- ☐ Seven registers, selected using address lines A0, A1, A2

Universal Asynchronous Receiver Transmitter (8250)

| Main input RS-232 handshaking lines: |                     |  |  |

|--------------------------------------|---------------------|--|--|

| Rl                                   | Ring Indicate       |  |  |

| DSR                                  | Data Set Ready      |  |  |

| CTS                                  | Clear To Send       |  |  |

| Main output RS-232 handshaking line  |                     |  |  |

| RTS                                  | Ready to Send       |  |  |

| DTR                                  | Data Terminal Ready |  |  |

| Serial Output                        |                     |  |  |

| SOUT                                 |                     |  |  |

| Serial Input                         |                     |  |  |

| SIN                                  |                     |  |  |

Universal Asynchronous Receiver Transmitter (8250)

| •                    |                                                        |  |

|----------------------|--------------------------------------------------------|--|

| Clock input:         |                                                        |  |

| XTAL1                | connect to a crystal to control the interal            |  |

| XTAL2                | clock oscillator (typically 1.8432 MHz)                |  |

| BAUDOT               | Baud rate (clock frequency / 16N; typically 9600 Baud) |  |

| Hardware interrupts: |                                                        |  |

| Reset<br>RESET       | active low                                             |  |

- Programming RS-232

- ☐ Main registers used in RS-232:

- Line Control Register (LCR)

- Line Status Register (LSR)

- Transmit and Receive Buffer (TD/RD)

- □ Base Address

- primary port (COM1:) 3F8h

- Secondary port (COM1:) 2F8h

- Standard PC can support up to four COM ports

- The base addresses are set in the BIOS memory; address of each port stored ad address locations:

```

0040 : 0000 (COM1:)

0040 : 0002 (COM2:)

0040 : 0004 (COM3:)

0040 : 0006 (COM4:)

```

```

#include <stdio.h>

#include <conio.h>

int main(void){

int far *ptr; /* 20-bit pointer */

ptr = (int far *) 0x0400000; /* 0040:0000 */

clrscr();

printf("COM1: %04x\n", *ptr);

printf("COM2: %04x\n", *(ptr+1));

printf("COM3: %04x\n", *(ptr+2));

printf("COM4: %04x\n", *(ptr+3));

return(0);

}

```

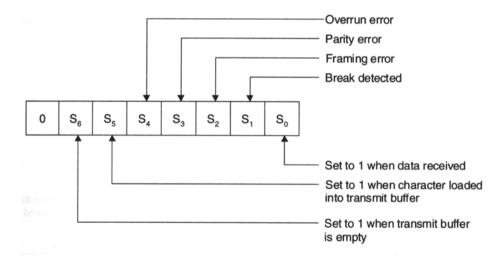

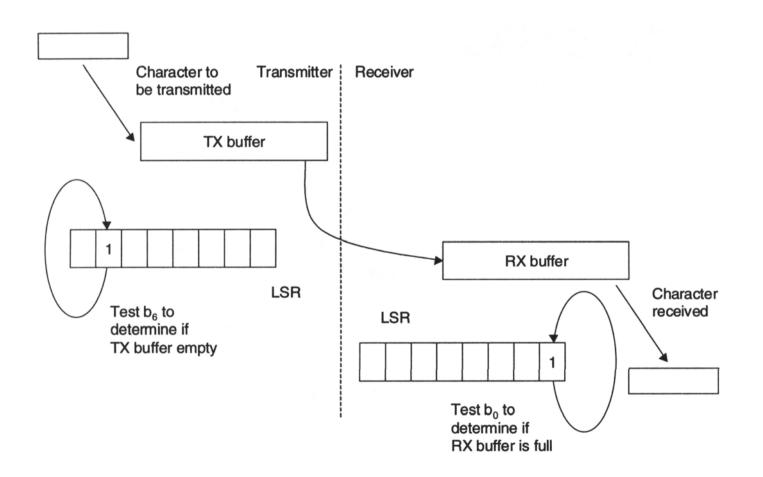

- Programming RS-232

- ☐ Line Status Register (LSR)

- Determines the status of the transmitter and receiver buffers

- Read-only; all bits set by hardware

Status bit S6 should be checked to see if the output buffer (TD/RD) is empty – i.e. data has been sent – before writing to the buffer

Copyright © 2007 David Vernon (www.vernon.eu)

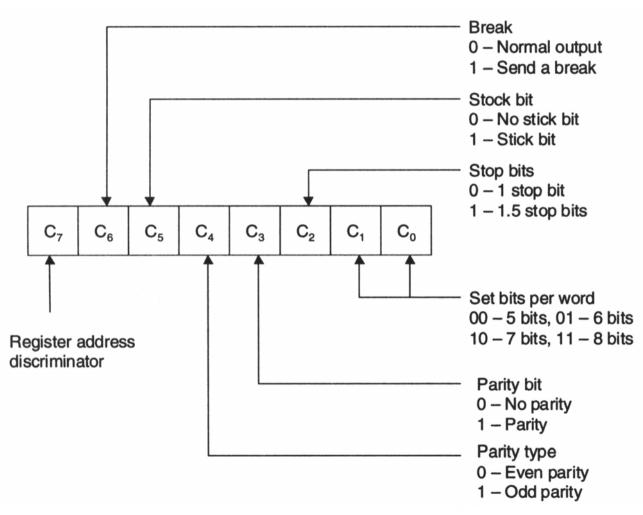

- Programming RS-232

- ☐ Line Control Register (LCR)

- Read/Write register

- Sets up communications parameters

- o Number of bits per character

- o Parity

- o Number of stop bits

- o Baud rate

# Serial Devices: UART

Copyrightine Control Register.eu)

### Serial Devices - UART

- Programming RS-232

- ☐ Line Control Register (LCR)

- Baud rate

- C7 set high to access the Baud rate divider

- (C7 set low to access the TR/RX buffer)

- Set baud rate by loading 16-bit divisor N

LSB (least significant byte) -> TR/RX buffer address

MSB (most significant byte)-> TR/RX buffer address + 1

- Value loaded depends on crystal frequency connected to the IC

Baud rate = Clock frequency / (16 \* N)

e.g., for 1.8432 MHz crystal frequency, 9600 baud, N = 1.8432E6 / (9600\*16) = 12 (000Ch)

# Serial Devices: UART

```

*/

send.c

#define TXDATA

0x3F8

#define LSR

0x3FD

#define LCR

0x3FB

#include<stdio.h>

#include <conio.h> /* included for getch

*/

*/

#include <dos.h>

/* included for inputb and outputb

void setup serial(void);

void send character(int ch);

int main(void)

int ch;

puts("Transmitter program. Please enter text (Cntl-D to end)");

setup_serial();

do

ch=getch();

send character(ch);

} while (ch!=4);

return(0);

```

```

void setup serial(void)

/* set up bit 7 to a 1 to set Register address bit

* /

outportb( LCR, 0x80);

*/

/* load TxRegister with 12, crystal frequency is 1.8432MHz

outportb(TXDATA, 0x0C);

outportb(TXDATA+1,0x00);

/* Bit pattern loaded is 00001010b, from msb to lsb these are:

*/

/* Access TD/RD buffer, normal output, no stick bit

*/

/* even parity, parity on, 1 stop bit, 7 data bits

* /

outportb(LCR, 0x0A);

void send_character(int ch)

char status;

/*repeat until Tx buffer empty ie bit 6 set*/

do {

status = inportb(LSR) & 0x40;

} while (status!=0x40);

outportb(TXDATA,(char) ch);

Copyright © 2007 David Vernon (www.vernon.eu)

```

```

*/

receive.c

#define TXDATA

0x3F8

#define LSR

0x3FD

#define LCR

0x3FB

#include <stdio.h>

#include <conio.h>

/* included for getch

*/

#include <dos.h>

/* included for inputb and outputb

* /

void

setup serial(void);

int

get character(void);

int main(void)

int inchar;

setup serial();

do

inchar=get_character();

putchar(inchar);

} while (inchar!=4);

return(0);

```

```

void setup serial(void)

/* set up bit 7 to a 1 to set Register address bit

* /

outportb( LCR, 0x80);

/* load TxRegister with 12, crystal frequency is 1.8432MHz

*/

outportb(TXDATA, 0x0C);

outportb(TXDATA+1,0x00);

Bit pattern loaded is 00001010b, from msb to lsb these are:

*/

*/

/*

Access TD/RD buffer, normal output, no stick bit

even parity, parity on, 1 stop bit, 7 data bits

* /

outportb(LCR, 0x0A);

int get_character(void)

int status;

/* Repeat until bit 1 in LSR is set */

status = inportb(LSR) & 0x01;

} while (status!=0x01);

return( (int)inportb(TXDATA));

Copyright © 2007 David Vernon (www.vernon.eu)

```

- Signal levels 0 to +5V

- Uses differential amplifiers at both transmitting and receiving ends to achieve high noise immunity

- Up to 10 Mbps over distance of 1.2km

- Motivation for the development of the USB

- Cost, configuration, and attachment of many peripheral devices to a PC creates problems

- □ Traditional interfacing (legacy systems)

- Peripherals mapped onto the I/O space

- o Although the I/O space has 64k of addressable locations (16 bits), legacy ISA bus PCs only decode 10 bit, leaving only 1k of I/O space

- o I/O address conflicts are common

- Assigned a specific IRQ (Interrupt Request line)

- o But there is a limited number of IRQs available (16)

- o Some of these are dedicated to specific devices

- o Some are shared (but not at the same time)

- Sometimes assigned a DMA (Direct Memory Access) channel

(Based in part on a summary written by Craig Peacock, www.beyondlogic.org)

- Motivation for the development of the USB

- ☐ Traditional interfacing (legacy systems)

- Physical limitation:

- o serial and parallel interfaces only support a single device each

- o Only solution is to add additional (expensive) expansion cards

- Usability

- o Too many connectors and/or cables

- o System must be shut down to attach most peripheral

- o System must be restarted to install/load software

#### USB Design Goals

- Single connector type for any peripheral

- Ability to attach many peripherals

- Ease system resource conflicts

- ☐ Hot plug support (hot-swapable)

- Automatic detection and configuration (plug-and-play)

- Dynamically loadable and unloadable drivers

- o Plug in device

- o Host detects device

- o Host interrogates device

- o Host loads appropriate driver

- Low-cost for both PC and peripheral

- Enhanced performance

- Support for new peripheral designs

- ☐ Support for legacy hardware and software

- Low-power implementation

- 650 pages in the definition of the USB 2.0 specification (see <a href="www.usb.org">www.usb.org</a>)

- USB 1.1 supported two speeds:

- ☐ Full speed 12 Mbit/s

- Low speed 1.5 Mbits/s

- Less susceptible to EMI (electromagnetic interference)

- Can use cheaper components

- USB 2.0 supports 480 Mbits/s

- High speed

- Competes with IEEE 1394 (Firewire) serial bus

- USB is host controlled

- Only one host per bus

- ☐ Host is responsible for

- undertaking all transactions

- Scheduling bandwidth

- Data can be sent by one of several transaction methods using a token-based protocol

- USB uses a tiered star topology

- Devices/peripherals can't be daisy-chained

- □ Need a hub

- Some peripherals have in-built hubs (e.g. keyboards)

- You can plug other devices into these

- Up to 127 devices can be connected to any one USB at any one given time 2007 David Vernon (www.vernon.eu)

- USB host controller specifications (USB 1.1)

- ☐ UHCI (Universal Host Controller Interface)

- Developed by Intel

- More work is done in software

- Hence cheaper hardware

- ☐ OHCE (Open Host Controller Interface)

- Developed by Compaq, Microsoft, and National Semiconductor

- More work done in hardware

- Hence simpler software!

- ☐ USB 2.0

- EHCI (Enhanced Host Controller Interface)

- USB Transfer modes

- ☐ Control

- □ Interrupt

- ☐ Bulk

- ☐ Isochronous

- Allows a device to reserve a defined amount of bandwidth with guaranteed latency

- Ideal for audio or video

- Avoids dropped frames due to congestion

#### Connectors

- ☐ Upstream connection to the host

- Downstream connection to a device

- Not interchangeable

- ☐ Type A plugs (and sockets) always face upstream to the host

- ☐ Type B plugs (and sockets) always face downstream to the peripheral device

- USB 2.0 includes mini-USB B connectors

### ◆ Connectors

| Pin Number | Cable Colour | Function                   |  |  |

|------------|--------------|----------------------------|--|--|

| 1          | Red          | V <sub>BUS</sub> (5 volts) |  |  |

| 2          | White        | D-                         |  |  |

| 3          | Green        | D+                         |  |  |

| 4          | Black        | Ground                     |  |  |

- Electrical Characteristics

- USB uses a differential transmission pair for data

- Differential '1' is transmitted by

- Pulling D+ over 2.8V

- Pulling D- under 0.3V

- ☐ Differential '0' is transmitted by

- Pulling D- over 2.8V

- Pulling D+ under 0.3V

- ☐ The polarity of the signal is inverted depending on the speed of the bus

- Use 'J' and 'K' to signify logic levels

- 'J' is differential 0 in low speed

- 'J' is differential 1 in high speed

#### Electrical Characteristics

- USB also uses single ended outputs (on D+, D-, or both)

- For example:

- Single Ended Zero (SE0)

- Used to signify a device reset if held for more than 10mS

- Generated by holding both D- and D+ low (<0.3V)</li>

- If you are building a USB interface / device, you can't get away with just sampling the differential output

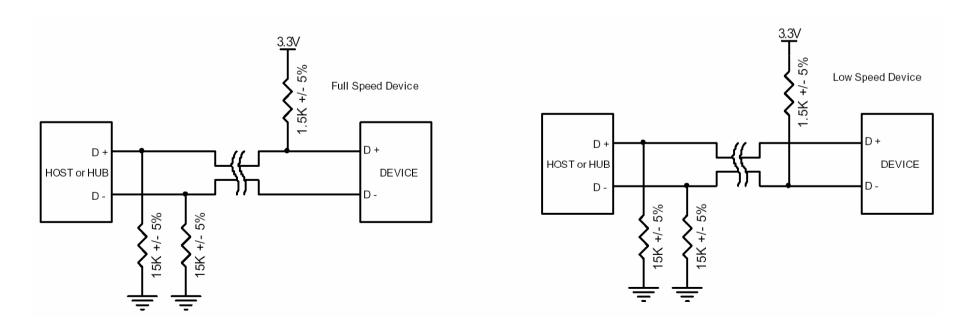

### Speed Identification

A USB device must indicate its speed by pulling either the D+ or D- line high to 3.3V (full speed and low speed respectively)

### Speed Identification

- High speed devices start by connecting as full speed

- Once attached, it does a high speed chirp (signal with a time-varying increase in frequency) during reset

- A high speed connection is then established if the hub supports it

#### Presence of a device on the bus

- ☐ These pull-up resistors are also used by the host or hub to detected the presence of a device connected to its port

- ☐ Without a pull-up resistor, USB assumes there is nothing connected to the bus

- Some devices have the resistor built into its silicon, which can be turned on and off under firmware control; others require an external resistor

Copyright © 2007 David Vernon (www.vernon.eu)

### Speed Identification

- → A USB 2.0 compliant device (downstream) is not required to support high-speed mode

- Allows cheaper devices to be produced if speed isn't critical

- Same is true for low speed USB 1.1 devices: don't have to support full speed

- ☐ High speed device MUST NOT support low speed mode

- Only support full speed (to establish connection) and high speed (if successfully negotiated with the host)

- □ A USB 2.0 compliant downstream facing device (hub or host) must support all three modes

- High speed 480 Mbits/s

- Full speed 12 Mbits/s

- Low speed 1.5 Mbits/s

#### Power Characteristics

- One big advantage of USB is that devices can be powerd by the bus (bus-powered devices)

- ☐ But there are restrictions

- USB devices specify power consumption in 2mA units in the configuration descriptor (later)

- A device cannot increase its power consumption over that specified during enumeration (set-up phase) EVEN IF IT LOSES EXTERNAL POWER

- 3 classes of USB power functions

- o Low-power bus powered functions

- o High-power bus powered functions

- o Self-powered functions

#### Power Characteristics

- Low-power bus powered functions

- Devices draw all its power from the V<sub>BUS</sub>

- Cannot draw more than one unit load (100mA)

- Must be designed to work with 4.40V <= V<sub>BUS</sub> <= 5.25V

- ☐ High-power bus powered functions

- Device draws all its power from the V<sub>BUS</sub>

- Cannot draw more than one unit load (100mA) until it has been configured

- Then it can draw 5 unit loads maximum, provided it requested it in its descriptor

- ☐ Self-powered functions

- May draw up to 1 unit load from the bus and derive the rest from an external source

- The 1 unit load allows detection and enumeration without external supply (but not operation)

### Suspend Mode

- Suspend mode is mandatory on all devices

- Suspend mode imposes further constraints on power

- ☐ The maximum suspend current is proportional to the unit load

- 1 unit load device: maximum suspend current is 500µA

- This is not a lot!

- The pull-up resistor (at the device, for detection) and pull-down resistor (at the host) will draw 200μA (3.3A / 16.5kΩ)

- 5V to 3.3V regulators to allow 3.3V devices to work will draw more

### Suspend Mode

- A USB device will enter suspend when there is no activity on the bus for greater than 3.0ms

- ☐ It then has a further 7ms to shutdown the device and draw no more than the suspend current

- ☐ To stay connected, the device must still provide power to the speed selection pull-up resistor during suspend

- USB can send 'start of frame' packets sent periodically to prevent an idle (no data) bus entering suspend

- High speed bus: frames sent every 124 μs

- Full speed bus: frames sent every 1ms

- Low speed bus: EOP (end of packet) every 1 ms

- □ A suspended device will resume operation when it receives any non-idle signalling.

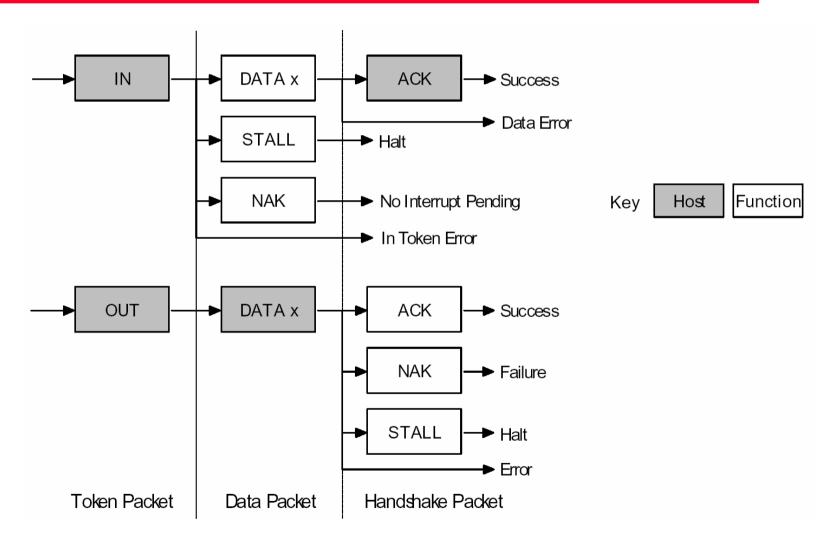

- USB Protocols Overview

- □ RS-232 serial interface does not define the format of the data being sent

- ☐ USB is made up of several layers of protocols

- ICs normally take care of the lower layer

- ☐ Each USB transaction consists of

- Token Packet (header defining what will follow)

- Optional Data Packet

- Status Packet (to acknowledge transaction & provide error correction)

- □ Remember: USB is host-centric the host initiates all transactions

- USB Protocols Overview

- ☐ Host generates token packet:

- Specifies what is to follow, and

- Whether the data transaction is a read or a write

- ☐ Host (usually) then sends a data packet

- Followed by a handshaking packet (check for errors)

- Note: data is transmitted LSB first

#### USB Packet Structure

- ☐ Each USB packet comprises the following fields

- Sync

- o 8 bits long

- o used to synchronize the clock of the receiver with the clock of the transmitter

- PID (Packet ID)

- o identifies the type of packet being sent

- o 4 bits (but complemented and repeated to give 8 bits)

- ADDR

- o Address of device to which packet is being sent

- o 7 bits (127 devices)

- o Address 0 is not valid

- any device which is not yet assigned an address must respond to packets sent to address zero

#### USB Packet Structure

- Each USB packet comprises the following fields

- ENDP

- o End point field

- o 4 bits (16 end-points)

- CRC

- o Cyclic Redundancy Check

- o Performed on all the data within the packet payload

- o Token packets have a 5 bit CRC

- o Data packets have a 16 bit CRC

- EOP

- o End of packet

- o Signalled by a Single Ended Zero (SE0) for approx. 2 bit times followed by a 'J' for 1 bit time

### USB Packet Structure - PID Values

| Group     | PID Value | Packet Identifier      |  |  |

|-----------|-----------|------------------------|--|--|

| Token     | 0001      | OUT Token              |  |  |

|           | 1001      | IN Token               |  |  |

|           | 0101      | SOF Token              |  |  |

|           | 1101      | SETUP Token            |  |  |

| Data      | 0011      | DATA0                  |  |  |

|           | 1011      | DATA1                  |  |  |

|           | 0111      | DATA2                  |  |  |

|           | 1111      | MDATA                  |  |  |

| Handshake | 0010      | ACK Handshake          |  |  |

|           | 1010      | NAK Handshake          |  |  |

|           | 1110      | STALL Handshake        |  |  |

|           | 0110      | NYET (No Response Yet) |  |  |

| Special   | 1100      | PREamble               |  |  |

|           | 1100      | ERR                    |  |  |

|           | 1000      | Split                  |  |  |

|           | 0100      | Ping                   |  |  |

| PID₀ | PID <sub>1</sub> | PID <sub>2</sub> | PID <sub>3</sub> | nPID₀ | nPID <sub>1</sub> | nPID <sub>2</sub> | nPID₃ |

|------|------------------|------------------|------------------|-------|-------------------|-------------------|-------|

|------|------------------|------------------|------------------|-------|-------------------|-------------------|-------|

- USB Packet Types

- ☐ USB has four packet types

- Token packets (type of transaction)

- Data Packets (payload / information)

- Handshake Packets (ack & error correction)

- Start of Frame packets (flag start of a new frame)

### USB Packet Types

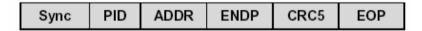

- Token packets

- 3 types of token packets

- In informs the USB device that host wishes to read info.

- Out Informs the USB device that host wishes to send info.

- Setup used to begin control transfers

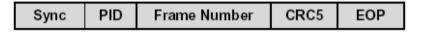

- Packet format:

- USB Packet Types

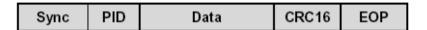

- Data packets

- 2 types of data packets

- Each can transmit 0-1023 bytes of data

- Data0

- Data1

- Packet format:

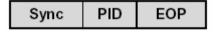

- USB Packet Types

- Handshake packets

- 3 types of handshake packets

- ACK Acknowledgement that the packet has been

- successfully received

- NAK

Reports that the device can neither send nor

- receive data

- STALL The device needs intervention from the host

- Packet format:

- USB Packet Types

- Start of Frame packets

- Consists of an 11-bit number & is sent by the host every 1mS

+/- 500nS

- Packet format:

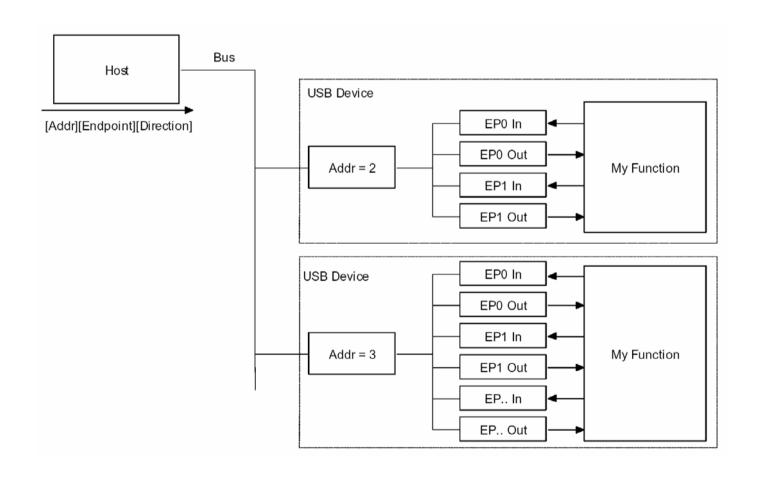

#### USB Functions

- ☐ USB functions are USB devices / peripherals (e.g. printers, disk drives, cameras, scanners, modems, ...)

- Most functions have a series of buffers, typically 8 bytes long

- ☐ Each buffer will belong to an endpoint

- EP0 IN

- EP0 OUT

- EP1 IN

- **-** ...

| <b>♦</b> | USB Functions - Conceptual Example |                                                                                                                                                                               |  |  |  |  |

|----------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          |                                    | Host sends a device descriptor request                                                                                                                                        |  |  |  |  |

|          |                                    | Function hardware reads the setup packet                                                                                                                                      |  |  |  |  |

|          |                                    | Function determines from the address field whether the packet is addressed to it                                                                                              |  |  |  |  |

|          |                                    | If it is, the function copies the payload of the following data<br>packet to the appropriate endpoint buffer (given by the<br>value in the endpoint field of the setup token) |  |  |  |  |

|          |                                    | Function then sends a handshake packet to acknowledge the reception of the byte                                                                                               |  |  |  |  |

|          |                                    | Function generates an internal interrupt for the appropriate endpoint, flagging that it has received a packet                                                                 |  |  |  |  |

|          |                                    | Typically, this is all done in hardware                                                                                                                                       |  |  |  |  |

|          |                                    | The software interrupt handler now reads the endpoint buffer, interprets it, and initiates the appropriate action                                                             |  |  |  |  |

#### Endpoints

- Sources or sinks of data

- Occur at the end of the communications channel at the USB function

- The endpoint OUT is where the host sends data to (on the function). E.g. **EP1 OUT**

- ☐ The endpoint IN is where the function places data when it is to be sent to the host, e.g. **EP1 IN**

- NB: the function cannot simply write to the bus the bus is controlled by the host and it must send an IN packet to enable the transfer of data from EP2 IN to the host

### Pipes

- A pipe is a logical connection between the host and the endpoint(s)

- Client software transfers data through pipes

- ☐ Pipes have a set of parameters associated with them

- How much bandwidth is allocated

- What transfer type it uses

- o Control

- o Bulk

- o Isochronous

- o Interrupt

- Direction of data flow

- Maximum packet/buffer size

- Default pipe is bidirectional, between EP0 IN and EP0 OUT with control transfer type

#### Pipes

- USB defines two types of pipes

- □ Stream Pipes

- No defined format

- Can send any type of data down a stream pipe

- Data flows sequentially

- Data has a predefined direction (in or out)

- Support bulk, isochronous, interrupt transfer types

- Can be controlled by either host or function / device

- Message Pipes

- Defined format

- Host controlled

- Initiated by a request sent from the host

- Data is then sent in the desired direction (depends on the request)

- Supports only control transfers

- Endpoint / Transfer Types

- Control Transfers

- Interrupt Transfers

- ☐ Isochronous Transfers

- □ Bulk Transfers

- ☐ Used for command and status operations

- ☐ E.g. to set up a USB device (enumeration)

- ☐ Initiated by the host

- ☐ Packet length

- 8 bytes low speed devices

- 64 bytes full speed devices

- 8, 16, 32, or 64 bytes high speed devices

- □ A Control Transfer can have up to three stages

- Setup Stage

- Data Stage

- Status Stage

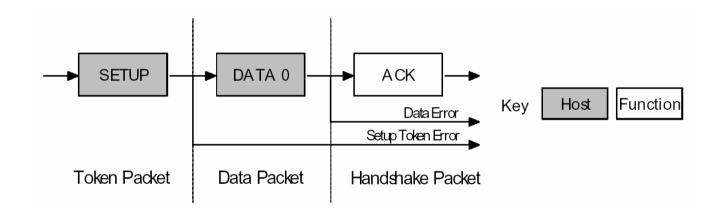

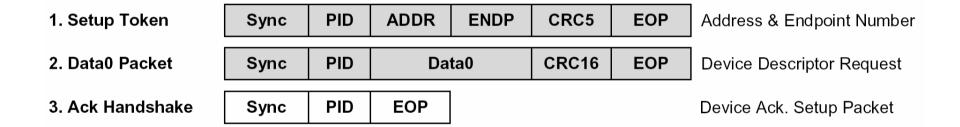

- □ Setup Stage

- Comprises 3 packets

- o Setup token

- contains address and endpoint number

- o Data packet

- always has PID of type Data0

- Contains a setup packet with the type of request

- o Handshake

- Acknowledge successful receipt or indicate and error

- If the function successfully receives the setup data (CRC and PID etc are okay), it responds with ACK

- Otherwise, it ignores the data and doesn't send a handshake

- Functions cannot issue STALL or NAK in response to a setup packet

- Control Transfers

- □ Setup Stage

- Data Stage (optional)

- The amount of data to be sent in this stage has been specified in the previous setup stage (in the setup packet)

- If the amount of data exceeds the maximum packet size, data is sent in multiple transfers (each of the maximum size except the last one)

- Two scenarios

- o IN direction

- o **OUT** direction

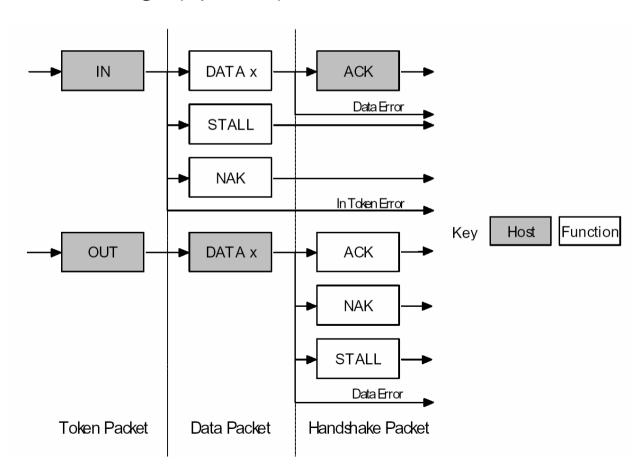

- □ Data Stage (optional)

- IN token issued when the host is ready to receive control data

- o If the function receives the **IN** token with an error, it ignores the packet

- o If the function receives the token correctly, it responds with either

- DATA packet (with the control data to be sent), or

- STALL packet (endpoint has had an error), or

- NAK packet (endpoint if working but has no data to send yet)

- ☐ Data Stage (optional)

- OUT token issued when the host needs to send the device a control data packet

- Followed by a DATA packet with the control data as a payload

- o If the function receives either the **OUT** token or the **DATA** packet with and error, it ignores the packet

- o Otherwise, it issues one of three responses

- ACK (if the function receives the data correctly successful transfer to the endpoint buffer)

- NAK (if the buffer was not empty e.g. still processing previous packet)

- STALL (endpoint has had an error)

#### Control Transfers

□ Data Stage (optional)

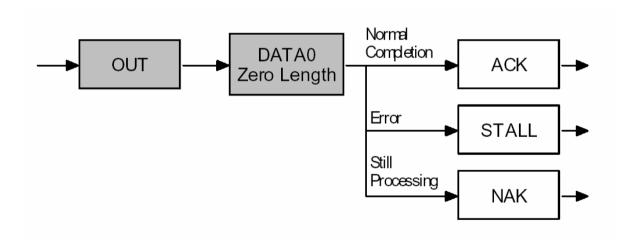

- □ Status Stage

- Reports the status of the overall request

- Varies depending on the direction of transfer

- Status reporting is always performed by the function

- IN

- o If the host sent **IN** token during the data stage to receive data, the host must acknowledge successful receipt of the data

- o Done by host sending an **OUT** token followed by a zero length data packet

- o Function can now report status

- ACK (success; ready for another command)

- STALL (error)

- NAK (still processing)

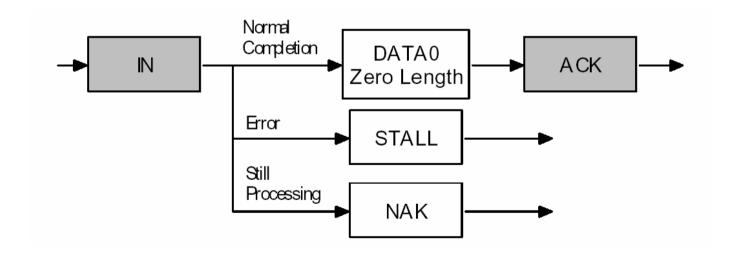

- Control Transfers

- □ Status Stage

- IN

- □ Status Stage

- OUT

- o If the host sent **OUT** token(s) during the data stage to transmit data, the function must acknowledge successful receipt of the data

- o Done by host sending an IN token

- o Function responds:

- DATA0 (success; ready for another command)

- STALL (error)

- NAK (still processing; host has to retry status stage later)

- o Host completes the stage by sending an ACK

- Control Transfers

- □ Status Stage

- OUT

### Control Transfer Example

- Host wants to request a device descriptor during enumeration

- ☐ Host sends Setup token (⇒ next packet is a setup packet)

- Address field will hold the address of the device / function

- Endpoint should be zero (⇒ default pipe)

- ☐ Host sends DATA0 packet

- 8 byte payload (containing device descriptor request; ch. 9 USB Specification)

- ☐ Device send **ACK** (or ignores it, if there is an error)

- ☐ This is the first USB transaction (setup stage): the device now decodes the 8 bytes received, determines it is a device descriptor request, & then attempt to send the descriptor. This is the next transaction (next slide)

### Control Transfer Example

- Assume the maximum payload size is 8 bytes

- ☐ Host now send IN token (tell device it can now send data)

- Device descriptor is sent in chunks of 8 bytes:

- Device sends DATA1 packet

- Host sends ACK handshake

- Host sends IN token

- Device sends DATA0 packet

- Host sends ACK handshake

- Host sends IN token

- Device sends **DATA1** packet (last 8 bytes of descriptor)

- Host send ACK handshake

- This is the second USB transaction (data stage)

| 1. In Token       | Sync | PID | ADDR    | ENDP | CRC5  | EOP | Address & Endpoint Number          |

|-------------------|------|-----|---------|------|-------|-----|------------------------------------|

| 2. Data1 Packet   | Sync | PID | Data1   |      | CRC16 | EOP | First 8 bytes of Device Descriptor |

| 3. Ack Handshake  | Sync | PID | EOP     |      |       |     | Host Acknowledges Packet           |

|                   |      |     |         |      |       |     |                                    |

| 1. In Token       | Sync | PID | ADDR    | ENDP | CRC5  | EOP | Address & Endpoint Number          |

| 2. Data0 Packet   | Sync | PID | Data0   |      | CRC16 | EOP | Second 8 bytes of Device Desc      |

| 3. Ack Handshake  | Sync | PID | EOP     |      |       |     | Host Acknowledges Packet           |

|                   |      |     |         | •    |       |     |                                    |

| 1. In Token       | Sync | PID | ADDR    | ENDP | CRC5  | EOP | Address & Endpoint Number          |

| 2. Data1/0 Packet | Sync | PID | Data0/1 |      | CRC16 | EOP | Last 8 bytes of Device Descriptor  |

| 3. Ack Handshake  | Sync | PID | ЕОР     |      |       |     | Host Acknowledges Packet           |

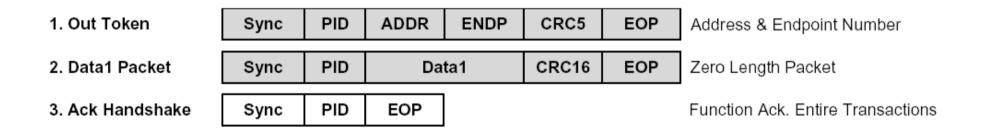

- Control Transfer Example

- ☐ Host sends **OUT** Token

- Host sends a zero length **DATA1** packet (overall transaction is successful)

- Device sends ACK handshake

- This is the third USB transaction (status stage)

#### Interrupt Transfers

- Under USB, if a device requires the attention of the host, it must wait until the host polls it before it can report it needs attention!

- ☐ Characteristics of Interrupt Transfers

- Guaranteed latency

- Stream pipe unidirectional

- Error detection and next period retry

- ☐ Typically non-periodic small device-initiated communication requiring bounded latency

- Maximum data payload

- 8 bytes low speed devices

- 64 bytes full speed devices

- 1024 bytes high speed devices

- Interrupt Transfers

- ☐ Interrupt IN Transaction

- Host will periodically poll the interrupt endpoint

- Polling rate is specified in the endpoint descriptor

- Host sends an IN token, the function respond with a DATA packet, and the host acknowledges

- ☐ Interrupt OUT Transaction

- When the host wants to send the device interrupt data

- Sends OUT token, followed by a data packet, and device acknowledges

| • | Iso | chronous Transfers                                                                                                           |  |  |  |  |  |  |  |

|---|-----|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|   |     | Occur continuously and periodically                                                                                          |  |  |  |  |  |  |  |

|   |     | Typically contain time sensitive information                                                                                 |  |  |  |  |  |  |  |

|   |     | ■ Audio                                                                                                                      |  |  |  |  |  |  |  |

|   |     | <ul><li>Video</li></ul>                                                                                                      |  |  |  |  |  |  |  |

|   |     | Characteristics of Isochronous Transfers                                                                                     |  |  |  |  |  |  |  |

|   |     | <ul> <li>Guaranteed access to USB bandwidth</li> </ul>                                                                       |  |  |  |  |  |  |  |

|   |     | <ul> <li>Bounded latency</li> </ul>                                                                                          |  |  |  |  |  |  |  |

|   |     | <ul> <li>Stream pipe – unidirectional</li> </ul>                                                                             |  |  |  |  |  |  |  |

|   |     | <ul><li>Error detection via CRC, but no retry or guarantee of delivery</li></ul>                                             |  |  |  |  |  |  |  |

|   |     | <ul><li>Full and high-speed modes only</li></ul>                                                                             |  |  |  |  |  |  |  |

|   |     | Maximum data payload is specified in the endpoint descriptor                                                                 |  |  |  |  |  |  |  |

|   |     | <ul> <li>1023 bytes – full speed devices</li> </ul>                                                                          |  |  |  |  |  |  |  |

|   |     | <ul><li>1024 bytes - high speed devices</li></ul>                                                                            |  |  |  |  |  |  |  |

|   |     | <ul> <li>Amount of data can be less than the pre-negotiated size and may vary<br/>from transaction to transaction</li> </ul> |  |  |  |  |  |  |  |

|   |     | No handshaking                                                                                                               |  |  |  |  |  |  |  |

|   |     | No error reports or STALL/HALT conditions                                                                                    |  |  |  |  |  |  |  |

#### Bulk Transfers

- ☐ Used for large bursty data transfer (e.g. printer, scanner)

- Characteristics of Bulk Transfers

- Error detection via CRC, with guarantee of delivery

- No guarantee of bandwidth or minimum latency

- Stream pipe unidirectional

- Full and high-speed modes only

- Maximum data payload

- 8, 16, 32, 64 bytes full speed devices

- 512 bytes high speed devices

- Amount of data can be less than the maximum packet size (zero padding not needed)

### Bandwidth Management

- ☐ The host is responsible for managing bandwidth

- Achieved at enumeration when configuring isochronous and interrupt endpoints (and throughout the operation of the bus)

- ☐ USB Specification Limits:

- Full speed bus: <= 90% allocated to periodic transfers</p>

- High speed bus: <= 80% allocated to periodic transfers

- Control transfer get allocated from the remainder

- Bulk transfers get what's left!

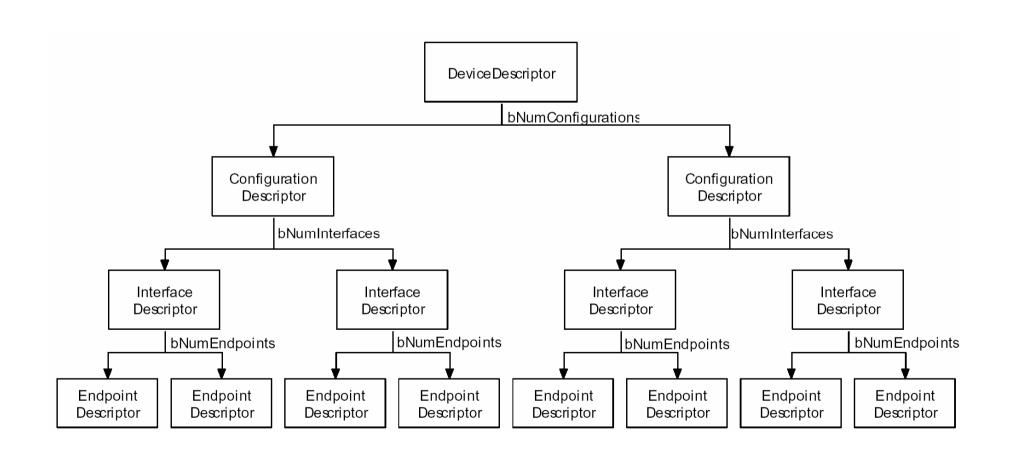

### USB Descriptors

- All USB devices define a hierarchy of descriptors

- What the device is

- What version of USB it supports

- How many ways it can be configuresd

- Number of end-points and their types

- ☐ Common descriptors

- Device descriptors

- Configuration descriptors

- Interface Descriptors

- Endpoint descriptors

- String descriptors

#### USB Descriptors

- Device Descriptor

- Only one of these

- USB revision compliance

- Product id and vendor id (needed to load the drivers)

- Number of configurations supported

- ☐ Configuration Descriptor

- Amount of power used

- Self- or bus-powered

- Number of interfaces

- Very few devices have more than one configuration

#### USB Descriptors

- Interface Descriptor

- Groups endpoints into functional groups

- Each functional group corresponds to a feature of the device

- For example, a fax/scanner/printer device might have three groups (and, hence, three interface descriptors)

- Endpoint Descriptors

- Describe endpoints other than endpoint zero

- Endpoint zero is always assumed to be a control endpoint

- □ String Descriptors

- Provide human readable information

- Optional

#### The Setup Packet

- Every USB device must respond to setup packets on the default pipe

- ☐ Used for detection and configuration of the device

- Setting USB device's address

- Requesting device descriptor

- Checking the status of an endpoint

- ☐ All requests have to be processed within set time limits

- ☐ Setup Packet is 8 bytes long

| Offset | Field         | Size | Value              | Description                                          |  |

|--------|---------------|------|--------------------|------------------------------------------------------|--|

| 0      | bmRequestType | 1    | Bit-Map            | D7 Data Phase Transfer Direction                     |  |

|        |               |      |                    | 0 = Host to Device                                   |  |

|        |               |      |                    | 1 = Device to Host                                   |  |

|        |               |      |                    | D65 Type                                             |  |

|        |               |      |                    | 0 = Standard                                         |  |

|        |               |      |                    | 1 = Class                                            |  |

|        |               |      |                    | 2 = Vendor                                           |  |

|        |               |      |                    | 3 = Reserved                                         |  |

|        |               |      |                    | D40 Recipient                                        |  |

|        |               |      |                    | 0 = Device                                           |  |

|        |               |      |                    | 1 = Interface                                        |  |

|        |               |      |                    | 2 = Endpoint                                         |  |

|        |               |      |                    | 3 = Other                                            |  |

|        |               |      |                    | 431 = Reserved                                       |  |

| 1      | bRequest      | 1    | Value              | Request                                              |  |

| 2      | wValue        | 2    | Value              | Value                                                |  |

| 4      | wIndex        | 2    | Index or<br>Offset | Index                                                |  |

| 6      | wLenght       | 2    | Count              | Number of bytes to transfer if there is a data phase |  |

oopyright & 2001 David vollon ( 111111 vollon.ou)

#### The Setup Packet

- □ bRequest field determines the request being made

- Standard device requests (section 9.4 of the USB specification)

- o Must be implemented for every USB device

- GET\_STATUS

- SET\_ADDRESS

- 6 more

- Class requests (e.g. communications class, mass storage class)

- Vendor defined requests

#### Enumeration

- The process of determining

- what device has just been connected to the bus

- The power requirements

- Number and type of endpoints

- Class of product

- ☐ Host then assigns an address to the device

- ☐ Host also enables a configuration allowing the device to transfer data on the bus

- ☐ See section 9.1.2 of the USB specification

- We have concentrated on the USB interface from the point of view of the device or function

- However, something has to manage all the transactions on the bus ... this is the job of the host

- We mentioned three USB host controller specifications

- UHCI (Universal Host Controller Interface)

- Developed by Intel

- More work is done in software

- Hence cheaper hardware

- OHCE (Open Host Controller Interface)

- Developed by Compag, Microsoft, and National Semiconductor

- More work done in hardware

- Hence simpler software!

- **USB 2.0**

- EHCI (Enhanced Host Controller Interface)

Copyright © 2007 David Vernon (www.vernon.eu)

- The job of each of these interfaces is to schedule transactions on the bus, based on the information provided by each function/device at enumeration

- Meet the needs of all isochronous, interrupt, control, and bulk transfers

- Transactions are generated by cycling through a list of frames (one frame every 1ms), each frame comprising a list of transfer descriptors

- Transfer descriptor

- USB device address

- Type of transaction to be performed

- Transfer size

- Speed of transaction

- Location of memory data buffer (where data will be read from or written to)

# The IEEE-488 Bus

- Digital Interface for Programmable Instrumentation

- Also known as the General Purpose Instrument Bus (GPIB)

- □ Provides a way of interconnecting a microcomputer controller with a large range of test and measuring instruments

- Signal generators, oscillocopes, network analysers ...

- ☐ The objective of the IEEE-488 bus is to enable different instruments using different data transfer rates, different message lengths, and different capabilities to communicate with each other on a single bus

- □ Allows a PC to supervise operation of instruments, and collect & process data they provide

Supports both star and daisy-chain topologies

Copyright © 2007 David Vernon (www.vernon.eu)

- ◆ In 1965, Hewlett-Packard designed the Hewlett-Packard Interface Bus (HP-IB) to connect their line of programmable instruments to their computers

- Because of its high transfer rates (nominally 1 Mbytes/s), this interface bus quickly gained popularity

- It was later accepted as IEEE Standard 488-1975, and has evolved to ANSI/IEEE Standard 488.1-1987

- ◆ Today, the name General Purpose Interface Bus (GPIB) is more widely used than HP-IB.

- ANSI/IEEE 488.2-1987 strengthened the original standard by defining precisely how controllers and instruments communicate

- ◆ The IEEE-488 interface bus is an 8 bit wide byte serial, bit parallel interface system which incorporates:

- 5 control lines (interface management)

- 3 handshake lines

- 8 bi-directional data lines.

- The entire bus consists of 24 lines, with the remaining lines occupied by ground wires.

- Uses negative logic with standard TTL levels

- When DAV is true, for example, it is a TTL low level (<= 0.8 V)</p>

- When DAV is false, it is a TTL high level (>= 2.0 V)

- ◆ The maximum data transfer rate is determined by a number of factors, but is assumed to be 1Mb/s.

- Devices exist on the bus in any one of 3 general forms:

- 1. Controller

- 2. Talker

- 3. Listener

- ◆ A single device may incorporate all three options, although only one option may be active at a time.

#### CONFIGURATION REQUIREMENTS

- To achieve the high data transfer rate for which the GPIB was designed, the physical distance between devices and the number of devices on the bus are limited

- A maximum separation of 4 m between any two devices and an average separation of 2 m over the entire bus

- ☐ A maximum total cable length of 20 m

- No more than **15 device** loads connected to each bus, with no less than two-thirds powered on

- The Controller makes the determination as to which device becomes active on the bus

- The GPIB can handle only one 'active' controller on the bus, although it may pass operation to another controller.

- Any number of active listeners can exist on the bus with an active talker as long as no more then 15 devices are connected to the bus

- The controller determines which devices become active by sending interface messages over the bus to a particular instrument

- ◆ Each individual device is associated with a 5 bit BCD code which is unique to that device.

- By using this code, the controller can coordinate the activities on the bus and the individual devices can be made to talk, listen (untalk, un-listen) as determined by the controller.

- A controller can only select a particular function of a device, if that function is incorporated within the device; for example a 'listen' only device can not be made to talk to the controller.

- The Talker sends data to other devices

- The Listener receives the information from the Talker

- Device dependent messages are moved over the GPIB in conjunction with the data byte transfer control lines

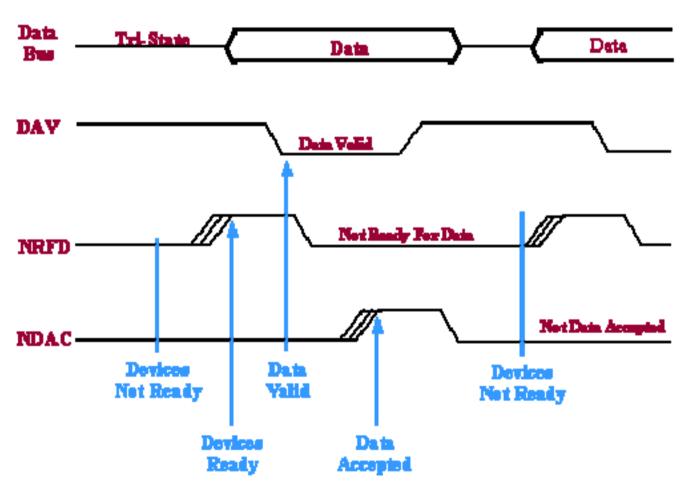

- These three lines (DAV, NRFD, and NDAC) are used to form a three wire 'interlocking' handshake which controls the passage of data

- ☐ The active talker would control the 'DAV' line (Data Valid)

- ☐ The listener(s) would control the 'NRFD' (Not Ready For Data), and the 'NDAC' (Not Data Accepted) line

- In the steady state mode the talker will hold 'DAV' high (no data available) while the listener would hold 'NRFD' high (ready for data) and 'NDAC' low (no data accepted

- After the talker placed data on the bus it would then take 'DAV' low (data valid)

- The listener(s) would then send 'NRFD' low and send 'NDAC' high (data accepted)

- Before the talker lifts the data off the bus, 'DAV' will be taken high signifying that data is no longer valid.

Copyright © 2007 David Vernon (www.vernon.eu)

- ◆ If the 'ATN' line (attention) is high while this process occurs the information is considered data (a device dependent message), but with the "ATN' line low the information is regarded as an interface message; such as listen, talk, un-listen or un-talk.

- The other five lines on the bus ('ATN' included) are the bus management lines

- These lines enable the controller and other devices on the bus to enable, interrupt, flag, and halt the operation of the bus

- Most devices operate either via front panel control or GPIB control (REMOTE)

- While using the front Panel the device is in the Local state, when receiving commands via the GPIB, the device is in the Remote state

- ◆ The device is placed in the Remote state when ever the System Controller is reset or powered on; also, when the system controller sends out an Abort message

- In addition, if the device is addressed, it then enters the Remote state.

| Pin | Signal Name | Function                | Pin | Signal Name | Function                |

|-----|-------------|-------------------------|-----|-------------|-------------------------|

|     |             |                         |     |             |                         |

| 1   | DIO1        | Data input/output bit 1 | 13  | DIO5        | Data input/output bit 5 |

| 2   | DI 02       | Data input/output bit 2 | 14  | DIO6        | Data input/output bit 6 |

| 3   | DIO3        | Data input/output bit 3 | 15  | DIO7        | Data input/output bit 7 |

| 4   | DIO4        | Data input/output bit 4 | 16  | DIO8        | Data input/output bit 8 |

| 5   | EOI         | End-or-identify         | 17  | REN         | Remote enable           |

| б   | DAV         | Data valid              | 18  | SHIELD      | Ground (DAV)            |

| 7   | NRFD        | Not ready for data      | 19  | SHIELD      | Ground (NRFD)           |

| 8   | NDAC        | Not data accepted       | 20  | SHIELD      | Ground (NDAC)           |

| 9   | IFC         | Interface clear         | 21  | SHIELD      | Ground (IFC)            |

| 10  | SRQ         | Service request         | 22  | SHIELD      | Ground (SRQ)            |

| 11  | ATN         | Attention               | 23  | SHIELD      | Ground (ATN)            |

| 12  | SHIELD      | Chassis ground          | 24  | SIGNALGND   | Signal ground           |

- NRFD: Not Ready For Data

- ☐ Part of a three wire handshake

- ☐ Used to indicate a device is ready for data, active low

- DAV: Data Valid

- ☐ Part of a three wire handshake

- Used to indicate valid data on the bus, active low

- NDAC: Not Data Accepted

- ☐ Part of a three wire handshake

- ☐ Used to indicate a device has not yet accepted data, active low

#### ATN: Attention

- ☐ When low (true) the system places all devices in Command Mode

- ☐ When high (false) the system places all devices in the Data Mode

- ☐ In Command Mode the Controller passes data to devices,

- ☐ In Data Mode the Talker passes data to the Listener.

- All devices must monitor the ATN line and respond within 200nS.

- ◆ EIO: End or Identify

- Indicates the last data transfer of a multi-byte sequence or used by the system controller to indicate a Parallel Poll to a device (in conjunction with the ATN line)

- ◆ IFC: Interface Clear;

- ☐ Used only by the system controller to halt current operations

- Placing all devices in an idle state

- ☐ All talkers are set to Un-talk and all Listeners are set to Un-listen

- Serial Poll is disabled

- All devices must monitor IFC, and respond within 100uS

#### ◆ REN: Remote Enable

- Used by the system controller to place devices in programming mode

- □ All Remote capable Listeners are set to remote operation (if they were addressed to Listen), when REN is true (low)

- ☐ When false, devices are set to Local control

- ☐ All device must monitor the REN line, and respond within 100uS.

- ◆ SRQ: Service Request

- Used by any device to indicate that a device needs service

- ☐ Any device may use this line

- Normally used as an interrupt line

- ☐ The controller may mask this line, in favor of Polling

- ☐ The SRQ line is cleared by a Serial Poll

- ◆ DIO1 to DIO8: Data Input-Output bus

- ☐ Bi-directional, Bite Serial-Byte Parallel.

- ☐ Per data line, bits are serial, ASCII data is sent as parallel data.

Standard data is 7 bit ASCII

- But no coding format is defined with IEEE-488.

- ◆ IEEE 488.2 AND SCPI

- ◆ The SCPI and IEEE 488.2 standards addressed the limitations and ambiguities of the original IEEE 488 standard

- ◆ IEEE 488.2 makes it possible to design more compatible and productive test systems

- ◆ The ANSI/IEEE Standard 488-1975, now called **IEEE 488.1**, greatly simplified the interconnection of programmable instrumentation by clearly defining mechanical, electrical, and hardware protocol specifications

- For the first time, instruments from different manufacturers were interconnected by a standard cable

- Although this standard went a long way towards improving the productivity of test engineers, the standard did have a number of shortcomings

- Specifically, IEEE 488.1 did not address data formats, status reporting, message exchange protocol, common configuration commands, or device-specific commands. As a result, each manufacturer implemented these items differently, leaving the test system developer with a formidable task.

- ◆ IEEE 488.2 enhanced and strengthened IEEE 488.1 by standardizing data formats, status reporting, error handling, Controller functionality, and common commands to which all instruments must respond in a defined manner

- By standardizing these issues, IEEE 488.2 systems are much more compatible and reliable

- The IEEE 488.2 standard focuses mainly on the software protocol issues and thus maintains compatibility with the hardware-oriented IEEE 488.1 standard

National Instruments: http://sine.ni.com/apps/we/nioc.vp?cid=1230&lang=US

National Instruments: http://sine.ni.com/apps/we/nioc.vp?cid=1230&lang=US

### IEEE-488 Bus

National Instruments: http://sine.ni.com/apps/we/nioc.vp?cid=1230&lang=US

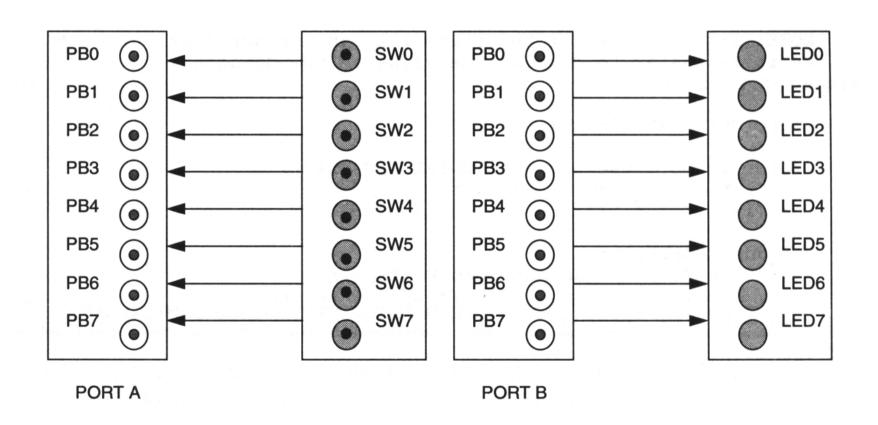

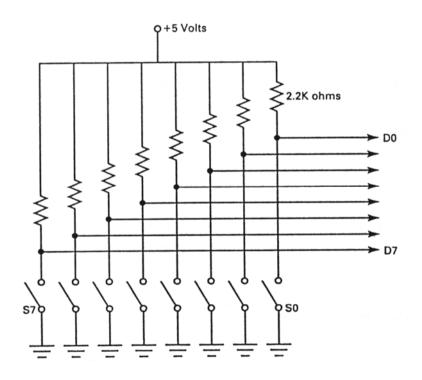

# Digitial Input/Output

- Digital input is the simplest form of inputting signals created by external devices to a computer

- Digital output is the simplest form of outputting from a computer to external control devices

- Digital input/output (I/O) provides for the inputting of digital logic signals to the computer from 'real-world' and outputting of compatible logic signals to the 'realworld'

- Typically uses an I/O Data Acquisition & Control (DA&C) board mapped on the PC bus to connect to switches, actuators, sensors, relays, lights, ...

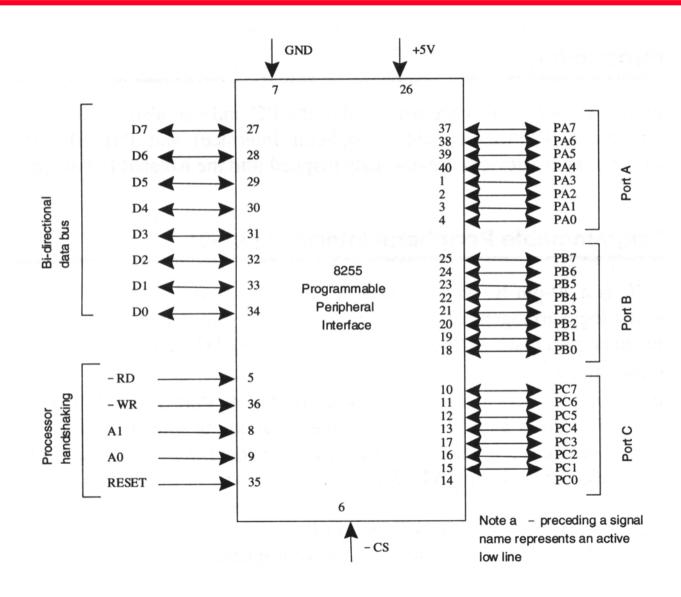

- Digital I/O can be achieved using the Programmable Peripheral Interface (PPI) device

- Intel 8255 IC

- □ 40 pins

- Normally mapped into the isolated I/O memory map of a PC

- ☐ TTL voltage compatibility (5.5V maximum input)

- Maximum current source / sink: 1mA

Connection to the system microprocessor is via the data bus (D0-D7), with handshaking lines:

- □ RD Read

- WR Write

- ☐ A1 Address line to select I/O port or control register

- □ A0

- ☐ RESET low input on RESET initializes the device

- ☐ CS chip select (low to activate the device)

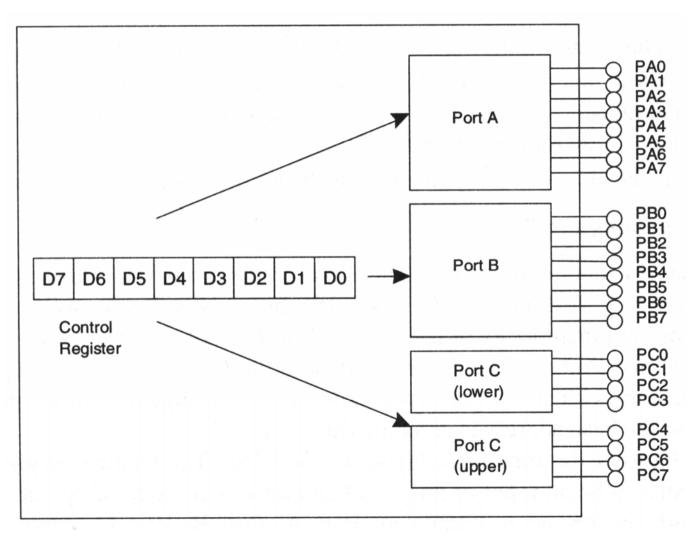

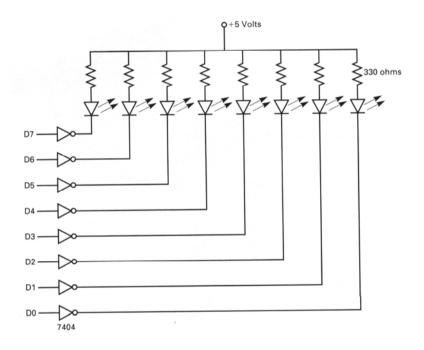

- ◆ 24 I/O lines, grouped into three groups of 8 bits

- ☐ Port A (address 00 [A1A0] BASE\_ADDRESS)

- □ Port B (address 01 BASE\_ADDRESS+1)

- □ Port C (address 10 BASE\_ADDRESS+2)

- Port C is divided into two parts: upper and lower

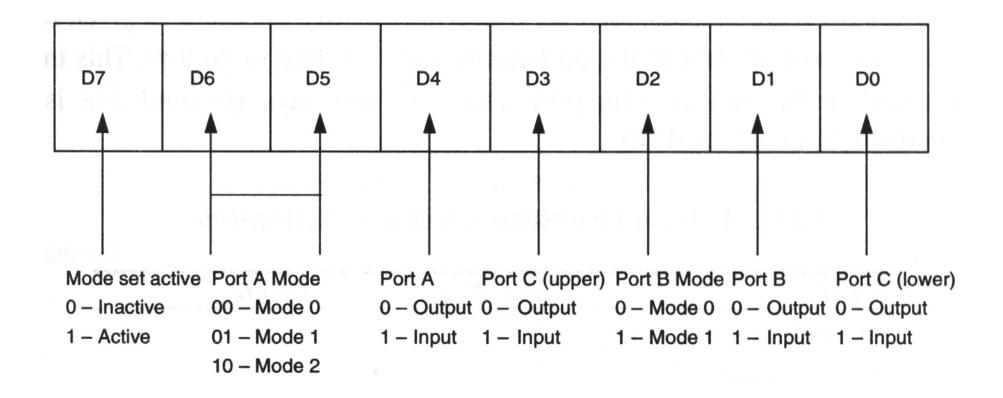

◆ Functionality programmed using the 8-bit Control Register (address 11 – BASE\_ADDRESS+3)

| D7 | 0      | inactive<br>active                                              |

|----|--------|-----------------------------------------------------------------|

| D4 | 0<br>1 | Port A is an output port<br>Port A is an input port             |

| D1 | 0<br>1 | Port B is an output port<br>Port B is an input port             |

| D0 | 0      | Port C lower is an output port<br>Port C lower is an input port |

| D3 | 0<br>1 | Port C upper is an output port<br>Port C upper is an input port |

Copyright © 2007 David Vernon (www.vernon.eu)

- Port A can be operated in one of three modes

(0, 1, 2) set by D6 & D5

- $\Box$  Mode 0 (D6 D5 = 00)

- Simplest mode: no handshaking

- Bits on Port C can be programmed as inputs or outputs

Port A can be operated in one of three modes

(0, 1, 2) set by D6 & D5

```

☐ Mode 1 (D6 D5 = 01)

```

- Handshaking for synchronization (required when speed of devices differs significantly)

- Port C is used for the handshaking signals

| - | Input:  |     |                                                                                                                           |

|---|---------|-----|---------------------------------------------------------------------------------------------------------------------------|

|   | o PC4   | STB | drive low to write data into Port A                                                                                       |

|   | o PC5   | IBF | Input Buffer Full; automatically goes high when data has been written into Port A & remains high until data has been read |

| • | Output: |     |                                                                                                                           |

| Output. |     |                                                                                    |

|---------|-----|------------------------------------------------------------------------------------|

| o PC7   | OBF | Output Buffer Full Port A, automatically goes low when data is written to the port |

|         |     | low whom data to written to the port                                               |

| o PC6   | ACK | drive low to acknowledge data has been                                             |

|         |     | read (and OBF then goes high again)                                                |

Copyright © 2007 David Vernori (www.vernon.eu)

- Port A can be operated in one of three modes

(0, 1, 2) set by D6 & D5

- Example: Port A input, mode 1 handshaking

- External device placed data on Port A data lines

- External device asserts STB (i.e. 0, driven low)

- Data is latched on port A register

- 8255 asserts IBF (i.e. 1, driven high)

- Example: Port A output, mode 1 handshaking

- CPU writes data to Port A

- OBF is asserted (i.e. 0, driven low)

- External device reads data on port A data lines

- External device asserts ACK (i.e. 0, driven low)

- OBF is cleared (i.e. 1, driven high)

- Port A can be operated in one of three modes

(0, 1, 2) set by D6 & D5

- ☐ Mode 2 (D6 D5 = 10)

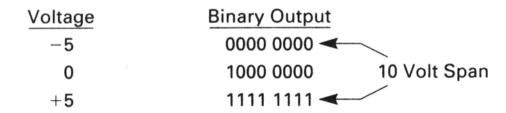

- Bi-directional I/O